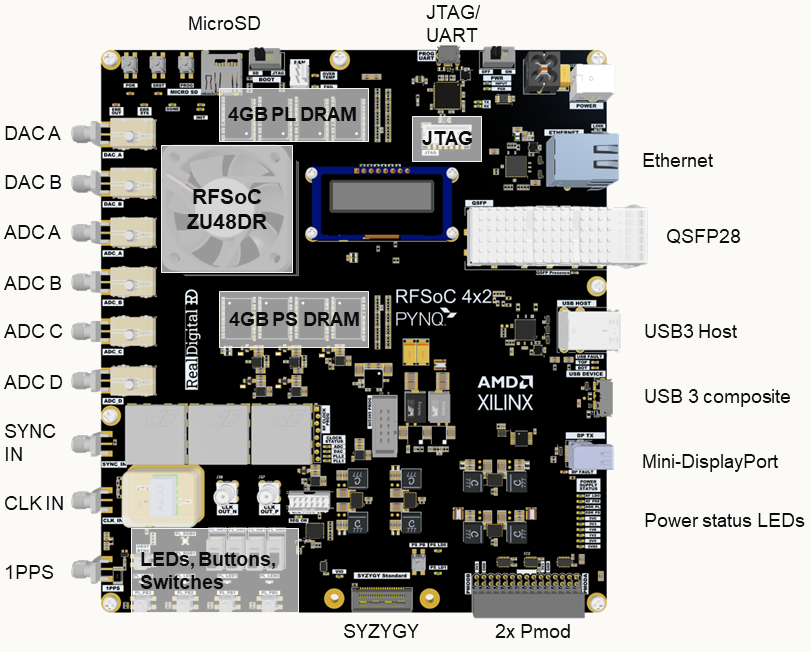

FPGA Overview:

RFSoC 4×2 Kit from Xilinx

ADCs with 5GSps and 14-Bit resolution.

DACs with 10GSps and 14-Bit resolution

QSFP28 interface for up to 100GB/s data transmission

Configuration via PS using Pynq (Quad Core ARM Cortex-A53 & Dual Core ARM Cortex-R5F)

GPIOs via SYZYGY and Pmod interface

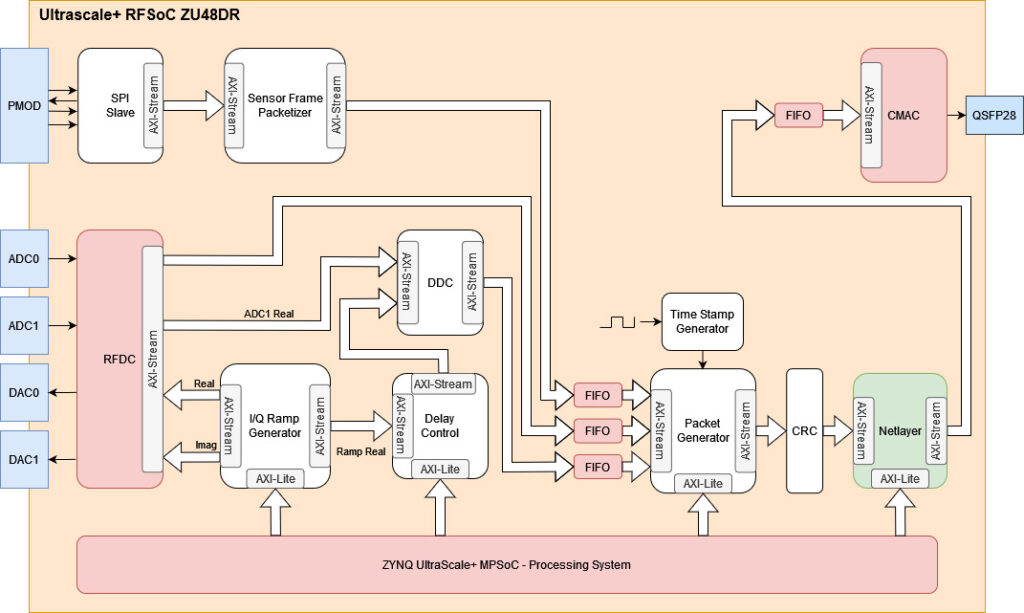

Block Diagram:

Processing system:

configure the signal processing chain

I/Q ramp generator:

creates FMCW rampes with customizable parameters

RFDC:

analog to AXI-Stream / AXI-Stream to analog

Delay control:

compensates delay of the RFDC

DDC:

digital down converter mixes Rx and Tx and decimates by 32

Packet Generator:

inserts meta data at the beginning of the packet and forwards data to CRC

CRC:

calculates checksum for data integrity

Netlayer:

stores the data into UDP, IP, Ethernet frame

CMAC:

signalling for 100GbE

SPI Slave:

receives data from companion board

Sensor Frame Packetizer:

adepts received data to desired format

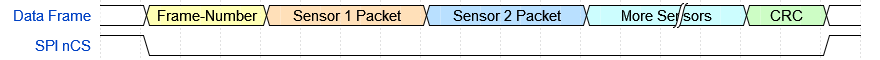

SPI protocol:

Timestamped sensor data from companion board developed by HGB bachelor project

Up to 50 MHz SPI

New data every 1 ms

Data integrity with CRC